During the Command Phase of the Seek operation the FDC is in the FDC BUSY state, but during the Execution Phase it is in the NON BUSY state. While the FDC is in the NON BUSY state, another Seek Command may be issued, and in this manner parallel seek operations may be done on up to 4 Drives at once.

If an FDD is in a NOT READY state at the beginning of the command execution phase or during the seek operation, then the NR (NOT READY) flag is set in Status Register 0 to a 1 (high), and the command is terminated.

Note that the 8272A Read and Write Commands do not have implied Seeks. Any R/W command should be preceded by: 1) Seek Command; 2) Sense Interrupt Status; and 3) Read ID.

#### RECALIBRATE

This command causes the read/write head within the FDD to retract to the Track 0 position. The FDC clears the contents of the PCN counter, and checks the status of the Track 0 signal from the FDD. As long as the Track 0 signal Is low, the Direction signal remains 1 (high) and Step Pulses are issued. When the Track 0 signal goes high, the SE (SEEK END) flag in Status Register 0 is set to a 1 (high) and the command is terminated. If the Track 0 signal is still low after 77 Step Pulses have been issued, the FDC sets the SE (SEEK END) and EC (EQUIP-MENT CHECK) flags of Status Register 0 to both 1s (highs), and terminates the command.

The ability to overlap RECALIBRATE Commands to multiple FDDs, and the loss of the READY signal, as described in the SEEK Command, also applies to the RECALIBRATE Command.

#### **SENSE INTERRUPT STATUS**

An Interrupt signal is generated by the FDC for one of the following reasons:

- 1. Upon entering the Result Phase of:

- a. Read Data Command

- b. Read a Track Command

- c. Read ID Command

- .d. Read Deleted Data Command

- e. Write Data Command

- f. Format a Cylinder Command

- g. Write Deleted Data Command

- h. Scan Commands

- 2. Ready Line of FDD changes state

- 3. End of Seek or Recalibrate Command

- 4. During Execution Phase in the NON-DMA Mode

Interrupts caused by reasons 1 and 4 above occur during normal command operations and are easily discernible by the processor. However, interrupts caused by reasons 2 and 3 above may be uniquely identified with the aid of the Sense Interrupt Status Command. This command when issued resets the interrupt signal and via bits 5, 6, and 7 of Status Register 0 identifies the cause of the interrupt.

Neither the Seek or Recalibrate Command have a Result Phase. Therefore, it is mandatory to use the Sense Interrupt Status Command after these commands to effectively terminate them and to provide verification of the head position (PCN).

Table 11. Seek, Interrupt Codes

|                        | SEEK END<br>BIT 5 | INTERRUPT CODE |       |                                                           |

|------------------------|-------------------|----------------|-------|-----------------------------------------------------------|

|                        |                   | BIT 6          | BIT 7 | CAUSE                                                     |

|                        | 0                 | 1              | 1 ,   | Ready Line changed state, either polarity                 |

|                        | 1                 | 0              | 0     | Normal Termination<br>of Seek or Recalibrate<br>Command   |

| Department of the last | 1                 | 1              | 0     | Abnormal Termination of<br>Seek or Recalibrate<br>Command |

#### SPECIFY

The Specify Command sets the initial values for each of the three internal timers. The HUT (Head Unload Time) defines the time from the end of the Execution Phase of one of the Read/Write Commands to the head unload state. This timer is programmable from 16 to 240 ms in increments of 16 ms (01 = 16 ms,  $02 = 32 \text{ ms} \dots \text{OF} =$ 240 ms). The SRT (Step Rate Time) defines the time interval between adjacent step pulses. This timer is programmable from 1 to 16 ms in increments of 1 ms (F = 1ms, E = 2 ms, D = 3 ms, etc.). The HLT (Head Load Time) defines the time between when the Head Load signal goes high and when the Read/Write operation starts. This timer is programmable from 2 to 254 ms in increments of 2 ms (01 = 2 ms, 02 = 4 ms, 03 = 6 ms... FE = 254 ms).

The step rate should be programmed 1 mS longer than the minimum time required by the drive.

The time intervals mentioned above are a direct function of the clock (CLK on pin 19). Times indicated above are for an 8 MHz clock, if the clock was reduced to 4 MHz (mini-floppy application) then all time intervals are increased by a factor of 2.

The choice of DMA or NON-DMA operation is made by the ND (NON-DMA) bit. When this bit is high (ND = 1) the NON-DMA mode is selected, and when ND = 0 the DMA mode is selected.

#### **SENSE DRIVE STATUS**

This command may be used by the processor whenever it wishes to obtain the status of the FDDs. Status Register 3 contains the Drive Status information.

#### INVALID

If an invalid command is sent to the FDC (a command not defined above), then the FDC will terminate the command. No interrupt is generated by the 8272A during this condition. Bit 6 and bit 7 (DIO and RQM) in the Main Status Register are both high ("1") indicating to the processor that the 8272A is in the Result Phase and the contents of Status Register 0 (ST0) must be read. When the processor reads Status Register 0 it will find an 80H indicating an invalid command was received.

A Sense Interrupt Status Command must be sent after a Seek or Recalibrate interrupt, otherwise the FDC will consider the next command to be an Invalid Command.

In some applications the user may wish to use this command as a No-Op command, to place the FDC in a standby or no operation state.

### 8272A

## Table 12. Status Registers

| 115            | BIT                | CVMPO  | DESCRIPTION                                                                                                                                                                                    |

|----------------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.            | NAME               | SYMBOL | a acologea a                                                                                                                                                                                   |

|                |                    | STATUS | S REGISTER 0                                                                                                                                                                                   |

| D <sub>7</sub> | Interrupt<br>Code  | IC     | $D_7 = 0$ and $D_6 = 0$<br>Normal Termination of Command,<br>(NT). Command was completed and<br>properly executed.                                                                             |

| D <sub>6</sub> |                    |        | $D_7$ = 0 and $D_8$ = 1<br>Abnormal Termination of Command, (AT). Execution of Command was started, but was not successfully completed.                                                        |

|                |                    |        | D <sub>7</sub> = 1 and D <sub>6</sub> = 0<br>Invalid Command issue, (IC).<br>Command which was issued was<br>never started.                                                                    |

|                |                    |        | D <sub>7</sub> = 1 and D <sub>6</sub> = 1<br>Abnormal Termination because<br>during command execution the<br>ready signal from FDD changed<br>state.                                           |

| D <sub>5</sub> | Seek End           | SE     | When the FDC completes the<br>SEEK Command, this flag is set to 1<br>(high).                                                                                                                   |

| D <sub>4</sub> | Equipment<br>Check | EC     | If a fault Signal is received from the FDD, or if the Track 0 Signal fails to occur after 77 Step Pulses (Recalibrate Command) then this flag is set.                                          |

| D <sub>3</sub> | Not Ready          | NR     | When the FDD is in the not-ready state and a read or write command is issued, this flag is set. If a read or write command is issued to Side 1 of a single sided drive, then this flag is set. |

| D <sub>2</sub> | Head<br>Address    | HD     | This flag is used to indicate the state of the head at Interrupt.                                                                                                                              |

| D <sub>1</sub> | Unit Select 1      | US 1   | These flags are used to indicate a                                                                                                                                                             |

| D <sub>0</sub> | Unit Select 0      | US 0   | Drive Unit Number at Interrupt                                                                                                                                                                 |

|                |                    | STATU  | S REGISTER 1                                                                                                                                                                                   |

| D <sub>7</sub> | End of<br>Cylinder | EN     | When the FDC tries to access a<br>Sector beyond the final Sector of a<br>Cylinder, this flag is set.                                                                                           |

| D <sub>6</sub> |                    |        | Not used. This bit is always 0 (low).                                                                                                                                                          |

| D <sub>5</sub> | Data Error         | DE     | When the FDC detects a CRC error in either the ID field or the data field, this flag is set.                                                                                                   |

| D <sub>4</sub> | Over Run           | OR     | If the FDC is not serviced by the<br>main-systems during data transfers,<br>within a certain time interval, this<br>flag is set.                                                               |

| $D_3$          |                    |        | Not used. This bit always 0 (low).                                                                                                                                                             |

| D <sub>2</sub> | No Data            | ND     | During execution of READ DATA,<br>WRITE DELETED DATA or SCAN<br>Command, if the FDC cannot find<br>the Sector specified in the IDR<br>Register, this flag is set.                              |

|                |                    |        | During executing the READ ID Com-<br>mand, if the FDC cannot read the<br>ID field without an error, then this<br>flag is set.                                                                  |

|                |                    |        | During the execution of the READ A<br>Cylinder Command, if the starting<br>sector cannot be found, then this<br>flag is set.                                                                   |

|                |                    |        |                                                                                                                                                                                                |

|                | BIT                                         |           |                                                                                                                                                                                                               |

|----------------|---------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.            | NAME                                        | SYMBOL    | DESCRIPTION                                                                                                                                                                                                   |

|                |                                             | STATUS RE | GISTER 1 (CONT.)                                                                                                                                                                                              |

| D <sub>1</sub> | Not<br>Writable                             | NW        | During execution of WRITE DATA, WRITE DELETED DATA or Format / Cylinder Command, if the FDC detects a write protect signal from the FDD, then this flag is set.                                               |

| Do             | Missing<br>Address<br>Mark                  | MA        | If the FDC cannot detect the ID<br>Address Mark after encountering the<br>index hole twice, then this flag is set                                                                                             |

|                |                                             |           | If the FDC cannot detect the Data<br>Address Mark or Deleted Data<br>Address Mark, this flag is set. Also<br>at the same time, the MD (Missing<br>Address Mark in Data Field) of<br>Status Register 2 is set. |

|                |                                             | STATUS    | REGISTER 2                                                                                                                                                                                                    |

| D <sub>7</sub> |                                             |           | Not used. This bit is always 0 (low).                                                                                                                                                                         |

| D <sub>6</sub> | Control<br>Mark                             | СМ        | During executing the READ DATA of SCAN Command, if the FDC encounters a Sector which contains a Deleted Data Address Mark, this flag is set.                                                                  |

| D <sub>5</sub> | Data Error in<br>Data Field                 | DD        | If the FDC detects a CRC error in the data field then this flag is set.                                                                                                                                       |

| D <sub>4</sub> | Wrong<br>Cylinder                           | wc        | This bit is related with the ND bit, and when the contents of C on the medium is different from that store in the IDR, this flag is set.                                                                      |

| D <sub>3</sub> | Scan Equal<br>Hit                           | SH        | During execution, the SCAN<br>Command, if the condition of<br>"equal" is satisfied, this flag is set                                                                                                          |

| D <sub>2</sub> | Scan Not<br>Satisfied                       | SN        | During executing the SCAN<br>Command, if the FDC cannot find a<br>Sector on the cylinder which meets<br>the condition, then this flag is set.                                                                 |

| D <sub>1</sub> | Bad<br>Cylinder                             | BC        | This bit is related with the ND bit, and when the content of C on the medium is different from that store in the IDR and the content of C is FF, then this flag is set.                                       |

| Do             | Missing<br>Address<br>Mark in Data<br>Field | MD        | When data is read from the medium<br>if the FDC cannot find a Data<br>Address Mark or Deleted Data<br>Address Mark, then this flag is set.                                                                    |

|                |                                             | STATU     | S REGISTER 3                                                                                                                                                                                                  |

| D <sub>7</sub> | Fault                                       | FT        | This bit is used to indicate the status of the Fault signal from the FDD.                                                                                                                                     |

| D <sub>6</sub> | Write<br>Protected                          | WP.       | This bit is used to indicate the status of the Write Protected signa from the FDD.                                                                                                                            |

| D <sub>5</sub> | Ready                                       | RDY       | This bit is used to indicate the statu of the Ready signal from the FDD.                                                                                                                                      |

| D <sub>4</sub> | Track 0                                     | ТО        | This bit is used to indicate the statu<br>of the Track 0 signal from the FDD.                                                                                                                                 |

| D <sub>3</sub> | Two Side                                    | TS        | This bit is used to indicate the statu<br>of the Two Side signal from the FDD                                                                                                                                 |

| D <sub>2</sub> | Head<br>Address                             | HD        | This bit is used to indicate the statu of Side Select signal to the FDD.                                                                                                                                      |

| D <sub>1</sub> | Unit Select 1                               | US 1      | This bit is used to indicate the statu of the Unit Select 1 signal to the FDC                                                                                                                                 |

| D <sub>0</sub> | Unit Select 0                               | US 0      | This bit is used to indicate the statu<br>of the Unit Select 0 signal to the FDC                                                                                                                              |

### **ABSOLUTE MAXIMUM RATINGS\***

Operating Temperature ................................0°C to +70°C Storage Temperature ..... -40°C to +125°C All Output Voltages ..... -0.5 to +7 Volts All Input Voltages ...... -0.5 to +7 Volts Supply Voltage V<sub>CC</sub> ..... -0.5 to +7 Volts

NOTICE: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification

## D.C. CHARACTERISTICS (T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +5V ± 10%)

|                  |                                        | Limits  |                       |          | Test                                                      |  |

|------------------|----------------------------------------|---------|-----------------------|----------|-----------------------------------------------------------|--|

| Symbol           | Parameter                              | Min.    | Max.                  | Unit     | Conditions                                                |  |

| VIL              | Input Low Voltage                      | . – 0.5 | 0.8                   | . V      |                                                           |  |

| -V <sub>IH</sub> | Input High Voltage                     | 2.0     | V <sub>CC</sub> + 0.5 | - V      |                                                           |  |

| V <sub>OL</sub>  | Output Low Voltage                     |         | 0.45                  | ٧        | I <sub>OL</sub> = 2.0 mA                                  |  |

| V <sub>OH</sub>  | Output High Voltage                    | 2.4     | Vcc                   | V        | $I_{OH} = -400  \mu A$                                    |  |

| Icc              | V <sub>CC</sub> Supply Current         | •       | 120                   | ′ mA     |                                                           |  |

| I <sub>IL</sub>  | Input Load Current<br>(All Input Pins) |         | 10<br>10              | μA<br>μA | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = 0V |  |

| - ILOH           | High Level Output<br>Leakage Current   | : : it  | 10                    | μА       | V <sub>OUT</sub> =V <sub>CC</sub>                         |  |

| lOFL             | Output Float<br>Leakage Current        |         | ±10                   | μΑ       | 0.45V ≤ V <sub>OUT</sub> ≤ V <sub>C</sub>                 |  |

### CAPACITANCE (T<sub>A</sub> = 25°C, f<sub>c</sub> = 1 MHz, V<sub>CC</sub> = 0V)

|                    |                          | Limits |      |        | Test                         |  |

|--------------------|--------------------------|--------|------|--------|------------------------------|--|

| Symbol             | Parameter                | Min.   | Max. | Unit - | Conditions                   |  |

| C <sub>IN(Φ)</sub> | Clock Input Capacitance  |        | 20   | . pF   | All Pins Except              |  |

| CIN                | Input Capacitance        |        | · 10 | pF     | Pin Under Test<br>Tied to AC |  |

| Cvo                | Input/Output Capacitance | _      | 20   | pF     | Ground                       |  |

### A.C. CHARACTERISTICS $(T_A = 0 \, ^{\circ}\text{C to} + 70 \, ^{\circ}\text{C}, V_{CC} = +5.0 \, ^{\circ}\text{to})$

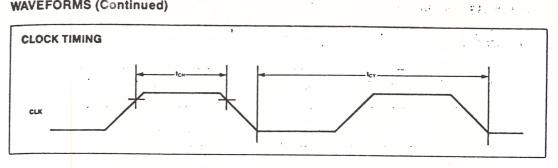

#### CLOCK TIMING

| Symbol | Parameter         | Min. | Max. | Unit | Notes     |

|--------|-------------------|------|------|------|-----------|

| tCY    | Clock Period .    | 120  | 500  | ns   | Note 5    |

| †CH    | Clock High Period | 40   |      | ns   | Note 4, 5 |

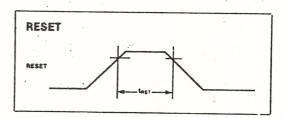

| †RST   | Reset Width       | 14   |      | tCY  |           |

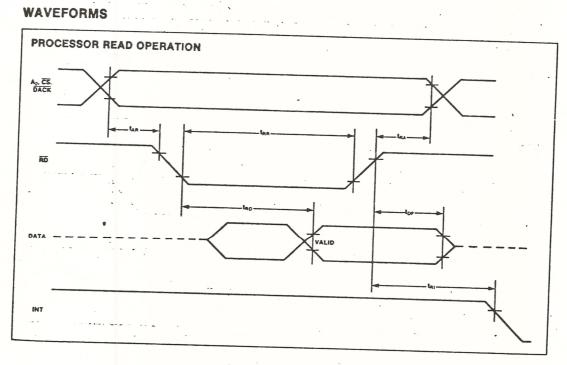

#### READ CYCLE

| tar | Select Setup to RD∔  | 0   |     | ns |  |

|-----|----------------------|-----|-----|----|--|

| tra | Select Hold from RDt | 0   |     | ns |  |

| trr | RD Pulse Width       | 250 |     | ns |  |

| tRD | Data Delay from RD+  |     | 200 | ns |  |

| tDF | Output Float Delay   | 20  | 100 | ns |  |

## .C. CHARACTERISTICS (Continued) (T<sub>A</sub>=0°C to +70°C, V<sub>CC</sub>= +5.0V ± 10%)

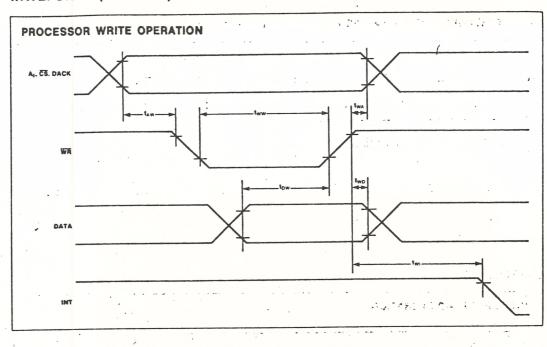

| VRITE CYCLE  | Parameter                                       | Typ.1  | Min.      | Max | Unit | Notes              |

|--------------|-------------------------------------------------|--------|-----------|-----|------|--------------------|

| Symbol       |                                                 |        | 0         |     | ns   |                    |

| AW           | Select Setup to WRI                             |        | 0         |     | ns   |                    |

| WA           | Select Hold from WRt                            |        | 250       |     | ns   |                    |

| haw          | WR Pulse Width                                  |        | 150       |     | ns   |                    |

| tDW          | Data Setup to WRt                               |        | 5         |     | ns   |                    |

| two          | Data Hold from WRt                              |        |           |     | -    |                    |

| NTERRUPTS    |                                                 | 7      | T         | 500 | ns   | Note 6             |

| tRi          | INT Delay from RDt                              |        |           | 500 | ns   | Note 6             |

| TWI          | INT Delay from WR1                              |        |           |     | 1    |                    |

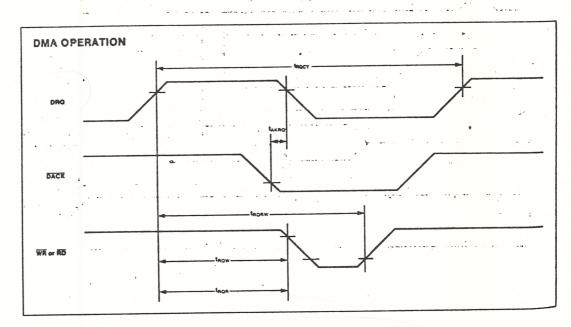

| )MA          |                                                 | -      |           |     |      | Note 6             |

| TROCY        | DRQ Cycle Period                                |        | 13        |     | μS   | NOTE 0             |

|              | DACK+ to DRQ+                                   |        |           | 200 | ns   | Note 6             |

| TROR         | DRO1 to RD4                                     |        | 800       |     | ns   | Note 6             |

|              | DRQ1 to WRI                                     |        | 250       |     | ns   | Note 6             |

| IROW         | DRQt to RDt or WRt                              |        |           | 12  | μs   | HOLE O             |

| IRORW        |                                                 |        |           |     |      |                    |

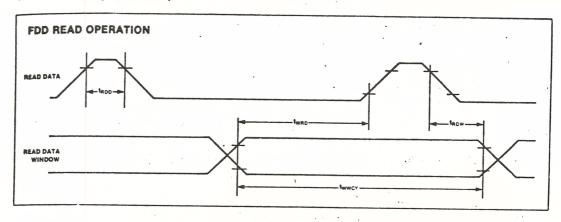

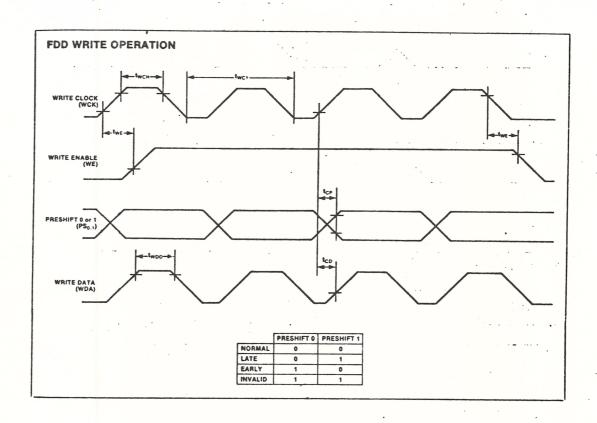

| FDD INTERFAC | WCK Cycle Time                                  | 2 or 4 |           |     | μѕ   | MFM = 0 Note 2     |

| PWCY         | WOR Cycle Time                                  | 1 or 2 |           |     | -    | MrM=1              |

|              | WCK High Time                                   | 250    | 80        | 350 | ns   |                    |

| TWCH         | Pre-Shift Delay from WCKf                       |        | 20        | 100 | ns   |                    |

| ICP .        | WDA Delay from WCKf                             |        | 20        | 100 | ns   |                    |

| #CD          | Write Data Width                                |        | tWCH - 50 |     | ns   |                    |

| PWDD         | WEt to WCKt or WEi to WCKi Delay                |        | 20        | 100 | ns   | 14514 0            |

| #WE          | Window Cycle Time                               | 2      |           |     | μS   | MFM = 0<br>MFM = 1 |

| *WWCY        | Villous Cytis                                   | 1      | 1         | -   | ns   |                    |

| twRD         | Window Setup to RDD1                            |        | 15        |     | ns   | -                  |

| IRDW         | Window Hold from RDD4                           |        | 15        |     | ns   |                    |

| tRDD         | RDD Active Time (HIGH)                          |        | 40        |     | 1    |                    |

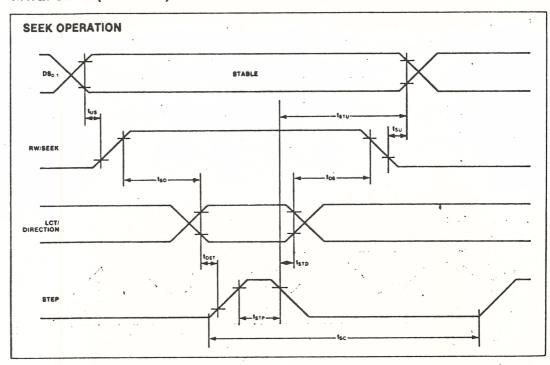

| FDD SEEK/DIR | ECTION/STEP                                     |        |           | 1   |      | Note 6             |

|              | US <sub>0,1</sub> Setup to RW/SEEKt             |        | 12        |     | μS   | Note 6             |

| ŧus          | US <sub>0,1</sub> Hold after RW/SEEK#           |        | 15        |     | μS   | -                  |

| tsu          | RW/SEEK Setup to LCT/DIR                        |        | 7         |     | μS   | Note 6             |

| tsD          | RW/SEEK Hold from LCT/DIR                       | •      | 30        |     | μS   | Note 6             |

| tDS          | LCT/DIR Setup to FR/STEPt                       |        | 1         |     | μS   | Note 6             |

| EDST         | LCT/DIR Hold from FR/STEP                       |        | - 24      |     | μS   | Note 6             |

| ISTD         | DS <sub>2,1</sub> Hold from FR/Step4            |        | 5         |     | μS   | Note 6             |

| tstu         | STEP Active Time (High)                         | 5      |           |     | μS   | Note 6             |

| tSTP         |                                                 |        | 33        |     | μS   | Note 3, 6          |

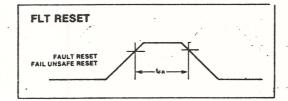

| tsc          | STEP Cycle Time  FAULT RESET Active Time (High) |        | 8         | 10  | μS   | Note 6             |

| tFR          | INDEX Pulse Width                               | 10     |           |     | tCY  | -                  |

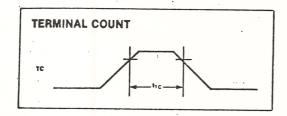

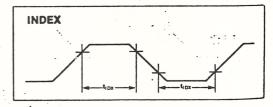

| tiDX         | Terminal Count Width                            |        | 1         |     | ICY  |                    |

| ITC          | 1 Terminal Cook Title                           |        |           |     |      |                    |

| MOTES:       | es for TA = 25°C and nominal supply voltage.    |        |           |     |      |                    |

- 3. tSC = 33 µs min. is for different drive units. In the case of same unit, tSC can be ranged from 1 ms to 16 ms with 8 MHz clock period, and 2 ms to 32 ms with 4 MHz clock, under software control.

- 5. At 4 MHz, the clock duty cycle may range from 16% to 76%. Using an 8 MHz clock the duty cycle can range from 32% to 52%. Duty cycle is defined as: D.C. = 100 (tCH + tCY) with typical rise and fall times of 5 ns.

- 6. The specified values listed are for an 8 MHz clock period. Multiply timings by 2 when using a 4 MHz clock period.

8272A

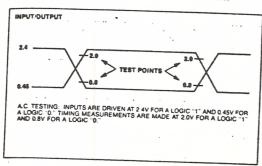

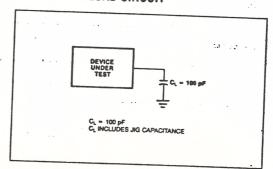

## A.C. TESTING INPUT, OUTPUT WAVEFORM

### A.C. TESTING LOAD CIRCUIT

6 dk = 1/2 µs

MANUAL DE CI's 1

intel

8272A

### **WAVEFORMS (Continued)**

13 ps -> DRQ

## WAVEFORMS (Continued)

8272A

## WAVEFORMS (Continued)

### 8272A

## WAVEFORMS (Continued)