# MANUAL DE CI's 1

# WESTERN DIGITAL

WD9216-00/WD9216-01 Floppy Disk Data Separator — FDDS

#### **FEATURES**

- PERFORMS COMPLETE DATA SEPARATION FUNCTION FOR FLOPPY DISK DRIVES

- SEPARATES FM OR MFM ENCODED DATA FROM ANY MAGNETIC MEDIA

- ELIMINATES SEVERAL SSI AND MSI DEVICES NORMALLY USED FOR DATA SEPARATION

- NO CRITICAL ADJUSTMENTS REQUIRED

- COMPATIBLE WITH WESTERN DIGITAL 179X, 176X AND OTHER FLOPPY DISK CONTROLLERS

- SMALL 8-PIN DUAL-IN-LINE PACKAGE

- +5 VOLT ONLY POWER SUPPLY

- TTL COMPATIBLE INPUTS AND OUTPUTS

# GENERAL DESCRIPTION

The Floppy Disk Data Separator provides a low cost solution to the problem of converting a single stream of pulses from a floppy disk drive into separate Clock and Data inputs for a Floppy Disk Controller.

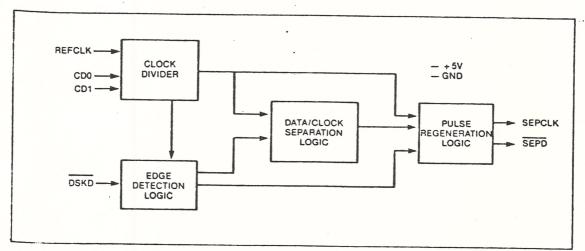

The FDDS consists primarily of a clock divider, a long-term timing corrector, a short-term timing corrector, and reclocking circuitry. Supplied in an 8-pin Dual-In-Line package to save board real estate, the FDDS operates on +5 volts only and is TTL compatible on all inputs and outputs.

The WD9216 is available in two versions; the WD9216-00, which is intended for 51/4" disks and the WD9216-01 for 51/4" and 8" disks.

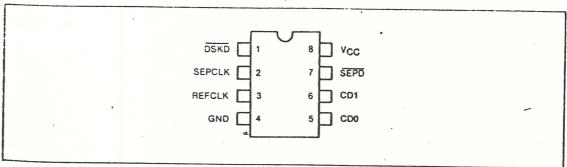

PIN CONFIGURATION

FLOPPY DISK DATA SEPARATOR BLOCK DIAGRAM

# MANUAL DE CI's 1

#### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS\***

| Operating Temperature Range 0°C to + | + 70°C |

|--------------------------------------|--------|

| Storage Temperature Range 55°C to    | 125°C  |

| Positive Voltage on any Pin,         |        |

| with respect to ground               | + 8.0V |

| Negative Voltage on any Pin,         |        |

| with respect to ground               | -0.3V  |

\* Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists it is suggested that a clamp circuit be used.

OPERATING CHARACTERISTICS (TA = 0°C to 70°C, VCC = +5V ± 5%, unless otherwise noted)

|                                                                        | PARAMETER                                                                                                                                                                | MIN.                                        | TYP.       | MAX.                              | UNITS                                    | COMMENTS                     |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-----------------------------------|------------------------------------------|------------------------------|

| INPUT<br>Low<br>Hig                                                    | ARACTERISTICS<br>VOLTAGE LEVELS<br>V Level VIL<br>h Level VIH                                                                                                            | 2.0                                         |            | 0.8                               | V                                        |                              |

| Lov<br>Hig                                                             | JT VOLTAGE LEVELS  / Level VOL  h Level VOH  CURRENT                                                                                                                     | 2.4                                         |            | 0.4                               | V                                        | IOL = 1.6mA<br>IOH = - 100µA |

| Lea                                                                    | kage I <sub>I</sub> L                                                                                                                                                    |                                             |            | 10                                | μΑ                                       | 0 < VIN < VDD                |

| Alli                                                                   | CAPACITANCE nputs R SUPPLY CURRENT                                                                                                                                       |                                             |            | 10                                | pF                                       |                              |

| IDD                                                                    |                                                                                                                                                                          |                                             |            | 50                                | mA                                       |                              |

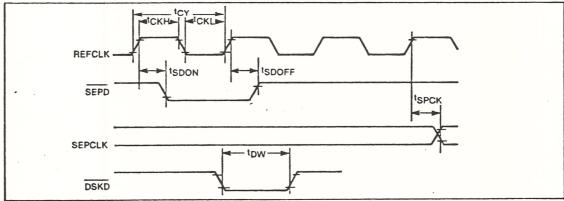

| A.C. CHA<br>Symbol                                                     | RACTERISTICS                                                                                                                                                             |                                             |            |                                   |                                          |                              |

| fCY<br>fCY<br>tCKH<br>tCKL<br>tSDON<br>tSDOFF<br>tSPCK<br>tDLL<br>tDLH | REFCLK Frequency REFCLK High Time REFCLK Low Time REFCLK to SEPD "ON" Delay REFCLK to SEPD "OFF" Delay REFCLK to SEPCLK Delay DSKD Active Low Time DSKD Active High Time | 0.2<br>0.2<br>50<br>50<br>100<br>0.1<br>0.2 | 100<br>100 | 4.3<br>8.3<br>2500<br>2500<br>100 | MHz<br>MHz<br>ns<br>ns<br>ns<br>ns<br>us | WD 9216-00<br>WD 9216-01     |

Figure 3. AC CHARACTERISTICS

### MANUAL DE CI's 1

# DESCRIPTION OF PIN FUNCTIONS

| PIN<br>NUMBER | PIN NAME        | SYMBOL   | FUNCTION                                                                                                                                                                           |

|---------------|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Disk Data       | DSKD     | Data input signal direct from disk drive. Contains combined clock and data waveform.                                                                                               |

| 2             | Separated Clock | SEPCLK   | Clock signal output from the FDDS derived from floppy disk drive serial bit stream.                                                                                                |

| 3             | Reference Clock | REFCLK   | Reference clock input.                                                                                                                                                             |

| 4             | Ground          | GND      | Ground.                                                                                                                                                                            |

| 5,6           | Clock Divisor   | CD0, CD1 | CD0 and CD1 control the internal clock divider circuit. The internal clock is a submultiple of the REFCLK according to the following table:  CD1 CD0 Divisor  0 0 1  0 1 2  1 0 4, |

| 7             | Separated Data  | SEPD     | SEPD is the data output of the FDDS                                                                                                                                                |

| 8             | Power Supply    | VCC      | + 5 volt power supply                                                                                                                                                              |

Figure 1.

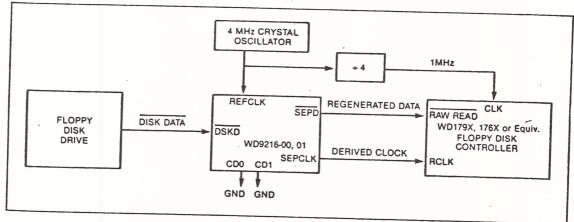

TYPICAL SYSTEM CONFIGURATION

(51/4 " Drive, Double Density)

# **OPERATION**

A reference clock (REFCLK) of between 2 and 8 MHz is divided by the FDDS to provide an internal clock. The division ratio is selected by inputs CD0 and CD1. The reference clock and division ratio should be chosen per table 1.

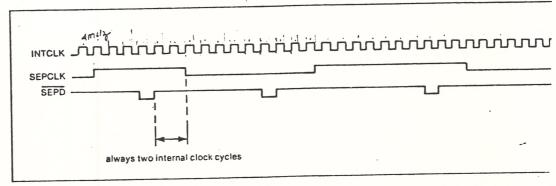

The FDDS detects the leading edges of the disk data pulses and adjusts the phase of the internal clock to provide the SEPARATED CLOCK output.

Separate short and long term timing correctors assure accurate clock separation.

The internal clock frequency is nominally 16 times the SEPCLK frequency. Depending on the internal timing correction, the internal clock may be a minimum of 12 times to a maximum of 22 times the SEPCLK frequency.

The reference clock (REFCLK) is divided to provide the internal clock according to pins CD0 and CD1.

WD9216-00/WD9216-01

TABLE 1: CLOCK DIVIDER SELECTION TABLE

|                        | 0.                    | OCK DIVIDEN   |             |             | g                   |

|------------------------|-----------------------|---------------|-------------|-------------|---------------------|

| DRIVE<br>(8" or 51/4") | DENSITY<br>(DD or SD) | REFCLK<br>MHz | CD1         | CD0         | REMARKS             |

| 8<br>8<br>8            | DD<br>SD<br>SD        | 8<br>8<br>4   | 0<br>0<br>0 | 0<br>1<br>0 | } Select either one |

| 5¼<br>5¼               | DD<br>DD              | 8 4           | 0           | 1 0         | Select either one   |

| 5¼<br>5¼<br>5¼         | SD<br>SD<br>SD        | 8<br>4<br>2   | 1<br>0<br>0 | 0<br>1<br>0 | Select any one      |

Figure 2.

See page 725 for ordering information.

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Corporation for its use; nor for any infringements of palents or other rights of third parties which may result from its use. No license is grainplication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to specifications at anytime without notice.